GHRD is a reference design for Intel System On Chip SoC FPGA. Open up the Altera bitfile format and design tools. Altera fpga design tools.

Altera Fpga Design Tools, The Arria II GZ FPGA family is based on 40-nm and combines low power with high performance and density. You will learn the steps in the standard FPGA design flow how to use Intel Alteras Quartus Prime Development Suite to create a pipelined multiplier and how to verify the integrity of the design using the RTL Viewer and by simulation using ModelSim. TI works closely with Altera to recommend the best power management solutions for a wide variety of applications such as embedded memory digital signal processing DSP blocks high-speed transceivers or high-speed IO pins. More information on the Intel FPGA Development tools is available from.

Altera Introduction To The Quartus Ii Software Documents Technical Library Element14 Community From community.element14.com

Altera Introduction To The Quartus Ii Software Documents Technical Library Element14 Community From community.element14.com

This will allow certain types of operations to be made faster in the datacenter - these might be referred to as big data operations but its not limited to that. Intel FPGA Altera Design Training Doulos delivers the best combination of HDL design flow tool and technology training modules to enable you to optimize your Intel FPGA based designs by. More information on the Intel FPGA Development tools is available from. Multi-Core AMP Development Tools for Altera Cyclone V SOC.

Linux UDP Real Time video streaming over LAN.

Read another article:

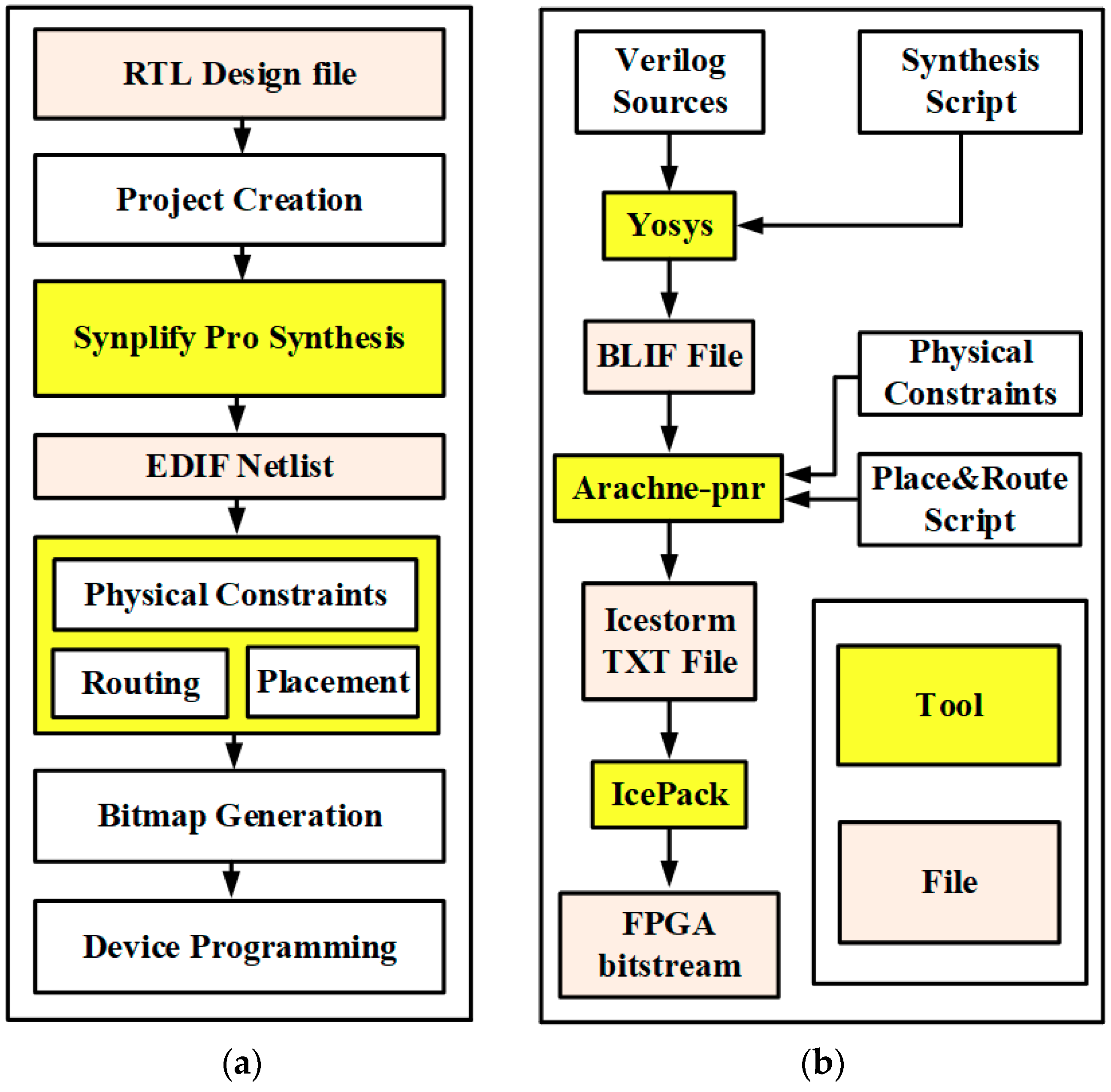

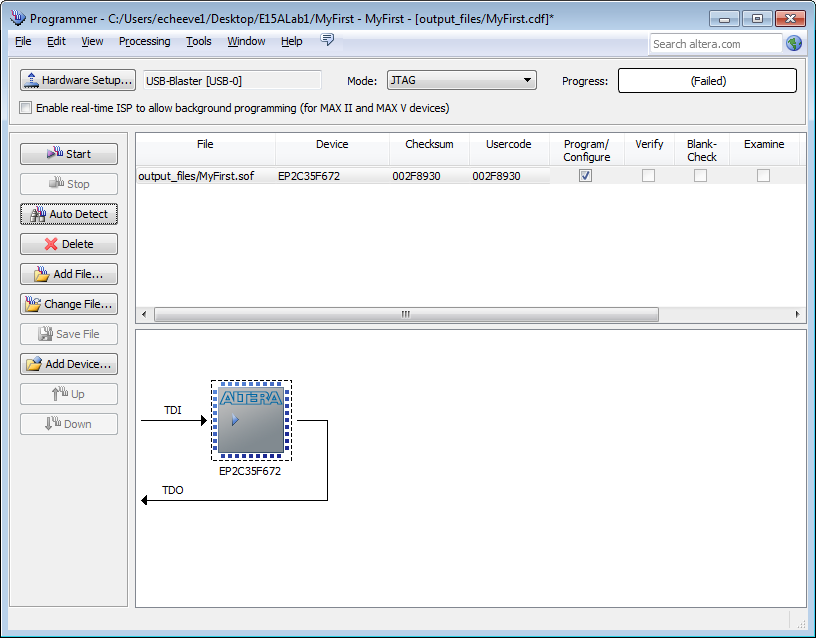

Doing this tutorial the reader will learn about. Basic FPGA Design Flow Using Command Line Scripting The ability to automate the FPGA design process saves time and increases productivity. Doing this tutorial the reader will learn about. Altera FPGA Design Expertise. 16 Altera Corporation My First FPGA Design Tutorial Assign the Device Figure 14.

Source: researchgate.net

Source: researchgate.net

Access and use Altera Arria II GZ FPGA devices in your designs. 3 Channel Video Mux and Display Controller. Finally we will use the software tool called the Altera Monitor Program to download the designed circuit into the FPGA device and download and execute a Nios II program that performs the desired task. It links all design files and performs technology mapping using the Quartus II TCL TCLQ script file. Accelerator Framework By Using An Intel Altera Xeon Fpga Fig 4 Shows Download Scientific Diagram.

Source: intel.la

Source: intel.la

This view allows step-by-step control over the entire FPGA design process enabling you to program and debug your system design on the FPGA. The Arria II GZ FPGA family is based on 40-nm and combines low power with high performance and density. This will allow certain types of operations to be made faster in the datacenter - these might be referred to as big data operations but its not limited to that. Choose Assignments Device. Digital Signal Processing Dsp Builder Intel Fpgas.

Source: vhdlwhiz.com

Source: vhdlwhiz.com

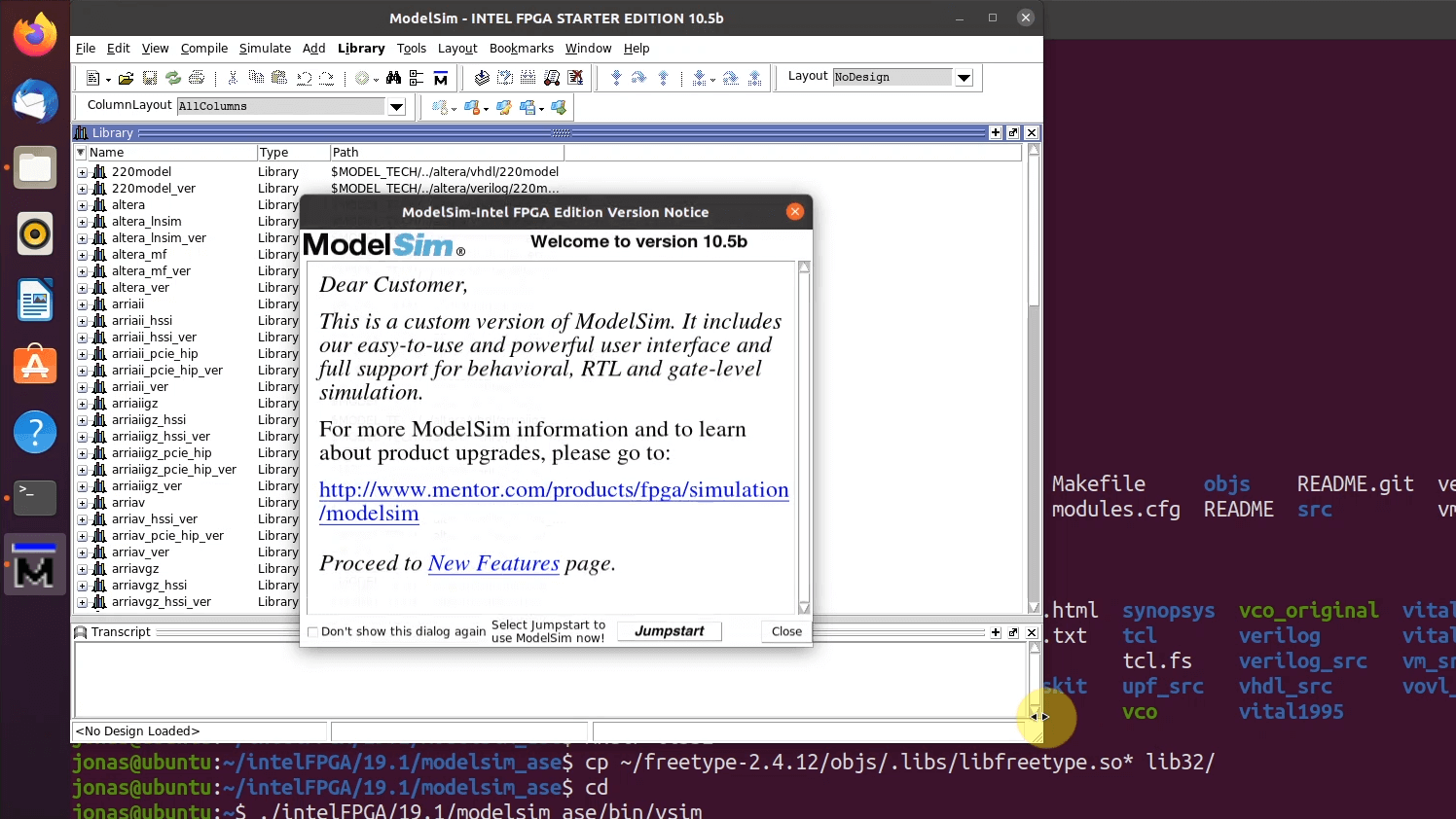

Download Quartus Prime software and any other software products you want to install into a temporary directory. Figure 1 shows the similarity between a typical command line implementation. Download device support files into the same directory as the Quartus Prime software installation file. Using Poly-Platform to deploy multicore application asymmetrically AMP on the Altera Cyclone V FPGA SoC ARM cores. How To Make Modelsim From Quartus Prime Lite Work On Ubuntu 20 04 Vhdlwhiz.

Source: intel.com

Source: intel.com

Multi-Core AMP Development Tools for Altera Cyclone V SOC. Open up the Altera bitfile format and design tools. Aldec has partnered with Altera to provide a seamless integration to our mutual customers in terms of device support libraries support and integration with GUI. Multi-Core AMP Development Tools for Altera Cyclone V SOC. Stratix Iv Fpga Design Tools Intel Fpgas.

Source: mouser.com

Source: mouser.com

3 Channel Video Mux and Display Controller. This stage creates the Altera project database and mapeqn file by running the Quartus II Analysis Synthesis Quartus_Map tool. The revolutionary Intel Quartus Prime Design Software includes everything you need to design for Intel FPGAs SoCs and complex programmable logic device CPLD from design entry and synthesis to optimization verification and simulation. 3 Channel Video Mux and Display Controller. Quartus Prime Design Software Intel Mouser.

Source: instructables.com

Source: instructables.com

I am more familiar with Xilinx ISE so I will check out the Altera Quartus tools online tutorials first. GHRD is a reference design for Intel System On Chip SoC FPGA. Altera Quartus II design software delivers the highest productivity and performance for Altera FPGAs CPLDs and HardCopy ASICs and offers the following design features to accelerate the design process. Qsys system integration tool. The Altera Fpga And Quartus Ii Software 23 Steps Instructables.

Source: mdpi.com

Source: mdpi.com

TI is the approved and tested vendor of power solutions for the Altera FPGAs and CPLDs. The Intel FPGA Development tools is an essential part of several CMC-supported FPGA-based Development System environments and is provided at no cost to Designer and Prototyping Subscribers to enable effective use of these systems. GHRD is a reference design for Intel System On Chip SoC FPGA. You will learn the steps in the standard FPGA design flow how to use Intel Alteras Quartus Prime Development Suite to create a pipelined multiplier and how to verify the integrity of the design using the RTL Viewer and by simulation using ModelSim. Electronics Free Full Text Recent Advances In Fpga Reverse Engineering Html.

Source: slideplayer.com

Source: slideplayer.com

Linux UDP Real Time video streaming over LAN. More information on the Intel FPGA Development tools is available from. The Altera project can be opened in Quartus if required. Choose Assignments Device. Chris Martin Member Technical Staff Embedded Applications Ppt Download.

Source: swarthmore.edu

Source: swarthmore.edu

TI is the approved and tested vendor of power solutions for the Altera FPGAs and CPLDs. Whether you are creating a complex FPGA design as a hardware engineer writing software for an embedded processor as a software developer modeling a digital signal processing DSP algorithm or focusing on system design Intel. Finally we will use the software tool called the Altera Monitor Program to download the designed circuit into the FPGA device and download and execute a Nios II program that performs the desired task. Using the Qsys tool to design a Nios II-based system. Quick Quartus From Schematics.

Source: embedded.com

Source: embedded.com

To assign th e device perform the following steps. Change the file permission for all the setup run files by. To assign th e device perform the following steps. The Arria II GZ devices include up to 24 6375-Gbps transceivers more density and memory and higher digital signal processing DSP capabilities than Arria II GX FPGAs. Tackle Team Based Fpga Design Embedded Com.

Source: slideplayer.com

Source: slideplayer.com

This will allow certain types of operations to be made faster in the datacenter - these might be referred to as big data operations but its not limited to that. Altera tools are integrated and accessed in the Altium Designer environment through the Devices view View Devices View. To assign th e device perform the following steps. Access and use Altera Arria II GZ FPGA devices in your designs. Chris Martin Member Technical Staff Embedded Applications Ppt Download.

Source: intel.la

Source: intel.la

The Arria II GZ devices include up to 24 6375-Gbps transceivers more density and memory and higher digital signal processing DSP capabilities than Arria II GX FPGAs. The Big 2 FPGA companies Altera Xilinx have. Using Poly-Platform to deploy multicore application asymmetrically AMP on the Altera Cyclone V FPGA SoC ARM cores. We think that this will be one of the most active battlegrounds over the next few years not just between the various FPGA companies but between FPGA companies and suppliers of traditional embedded processing platforms. Nios Ii Processors Design Tools.

Source: slideplayer.com

Source: slideplayer.com

Given the relative FPGA capacity and feature set offered by both vendors this chapter emphasizes replacement of Cyclone. It links all design files and performs technology mapping using the Quartus II TCL TCLQ script file. More information on the Intel FPGA Development tools is available from. Open up the Altera bitfile format and design tools. Fpga Devices Fpga Design Flow Ppt Video Online Download.

Source: aldec.com

Source: aldec.com

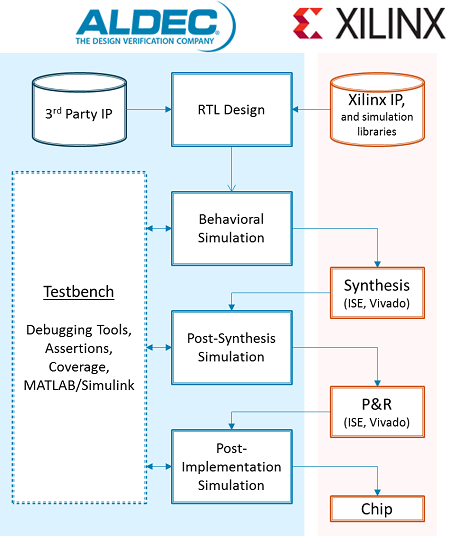

TI is the approved and tested vendor of power solutions for the Altera FPGAs and CPLDs. Access and use Altera Arria II GZ FPGA devices in your designs. FPGA Design Guide 3 2 Moving Designs from Altera The guidelines in this chapter provide practical advice for Altera users who want to migrate designs originally created for Altera FPGAs to Lattice Semiconductor devices. Using the Qsys tool to design a Nios II-based system. Xilinx Fpga Design Flow.

Source: community.element14.com

Source: community.element14.com

Altera FPGA Design Expertise. Aldec has partnered with Altera to provide a seamless integration to our mutual customers in terms of device support libraries support and integration with GUI. I will compare the online training offerings of Altera and Xilinx. This stage creates the Altera project database and mapeqn file by running the Quartus II Analysis Synthesis Quartus_Map tool. Altera Introduction To The Quartus Ii Software Documents Technical Library Element14 Community.